According to data shared by industry insider Jaykihn, the Nova Lake-S desktop lineup will feature a sophisticated multi-tile architecture. The most prominent feature of this new generation is the inclusion of specialized bLLC variants, which are designed to offer substantially higher cache capacities than standard compute tiles. Specifically, Intel is reportedly developing single-tile configurations with up to 144 MB of cache and dual-tile configurations that reach a staggering 288 MB. This move signals a departure from incremental cache increases, moving instead toward a massive pool of on-die memory to minimize data latency and improve instructions-per-clock (IPC) efficiency.

Architectural Framework and Die Configurations

The Nova Lake-S architecture is built upon a modular design comprising five primary die configurations. These dies are categorized into single compute tile and dual compute tile flavors, with the latter designated as "DS" (Dual Slot or Dual Stack) variants intended for the enthusiast market. The entry-level segment will utilize an 8-core die (8C), consisting of 4 Performance-cores (P-cores) and 4 Low-Power Efficiency-cores (LPE-cores). Stepping up, the 16-core (16C) variant integrates 4 P-cores, 8 E-cores, and 4 LPE-cores.

The mid-to-high-range market will be served by two distinct 28-core (28C) die flavors. Both feature an 8P+16E+4LPE configuration, but they differ in their cache implementation. One utilizes a standard cache layout, while the other incorporates the specialized bLLC design. The physical footprint of these dies reflects the added complexity: the standard 28C compute tile measures approximately 98mm², whereas the bLLC-equipped version expands to 154mm². This 57% increase in die area is almost entirely dedicated to the expanded cache structures.

At the absolute peak of the stack sits the 52-core (52C) "DS" variant. This enthusiast-grade processor utilizes two compute tiles, each housing 8 P-cores and 16 E-cores. Interestingly, the LPE-cores are not doubled in this configuration; the 4 LPE-cores reside outside the primary compute tiles, likely on the SoC (System on Chip) tile, maintaining a consistent count across the high-end lineup.

The Core Ultra Series 4 SKU Roadmap

Intel’s preliminary roadmap for the Nova Lake-S family suggests a diverse lineup spanning the Core Ultra 3, 5, 7, and 9 brands, along with a new "Enthusiast" tier that may carry a "Core Ultra X" or similar premium designation. The flagship model, identified by the product ID P3DX, is expected to feature 52 cores and the full 288 MB of bLLC cache. This processor is rumored to operate with a Thermal Design Power (TDP) of 175W, though peak power consumption during burst workloads could significantly exceed this figure.

Below the flagship, a 44-core model (P2DX) is planned, featuring two tiles with an 8P+12E configuration and 264 MB of bLLC cache. The Core Ultra 9 tier will include a 28-core model with 144 MB of cache at a 125W TDP. For more power-efficient builds, Intel is preparing 65W and 35W variants, including a 22-core Core Ultra 9 and various Core Ultra 7 and 5 models. Notably, even the entry-level Core Ultra 3 (T1) will feature 6 cores (2P+4LPE), ensuring that the entire stack benefits from the architectural improvements of the Nova Lake generation.

Integrated graphics across the Nova Lake-S lineup will be powered by the Xe3 architecture. Most SKUs are expected to feature 2 Xe3 cores, providing basic display and media acceleration capabilities, although reports suggest at least one specific SKU may feature a more robust iGPU configuration for users who do not require a discrete graphics card.

Comparative Analysis: Intel bLLC vs. AMD 3D V-Cache

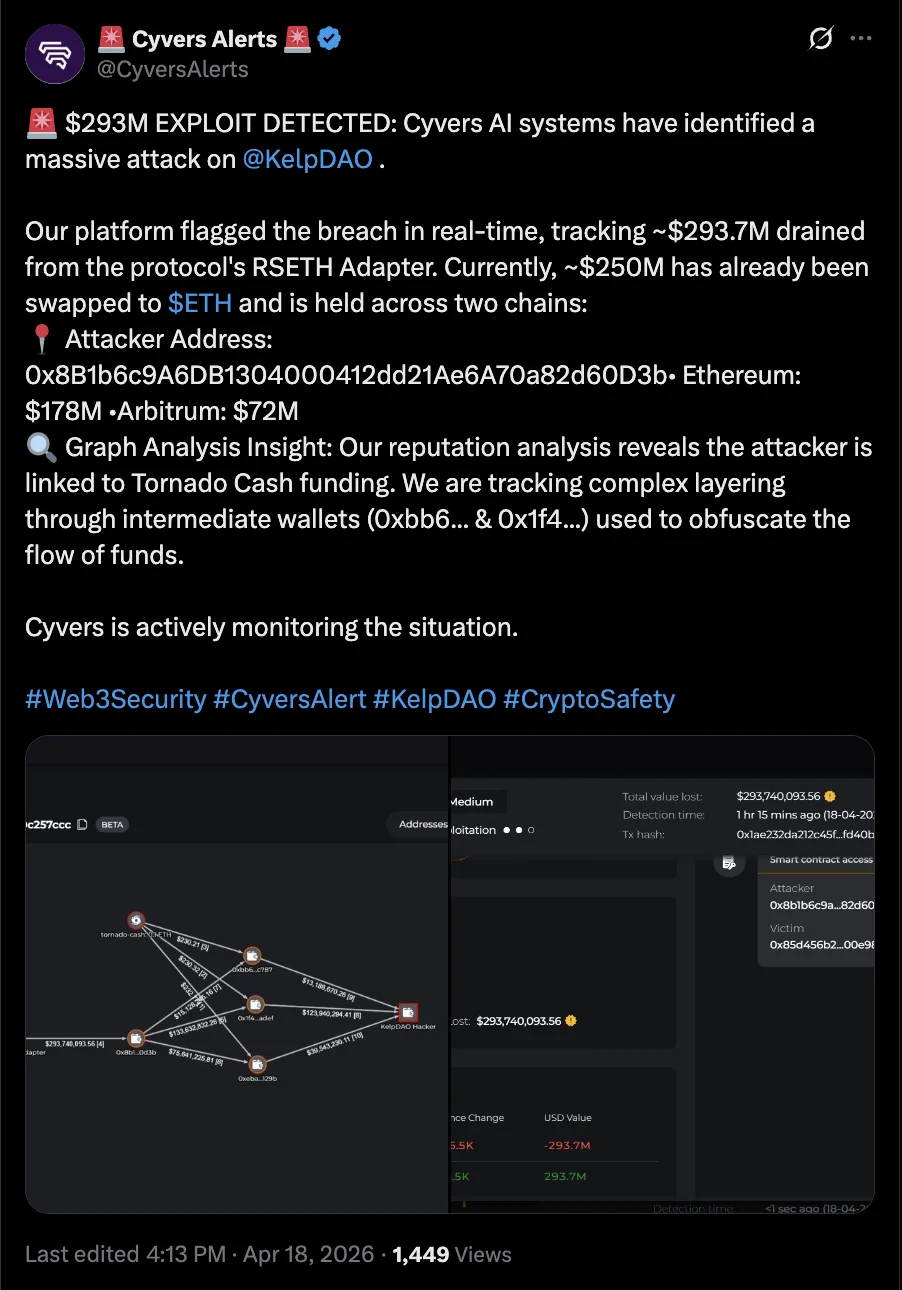

The primary motivation behind the bLLC initiative is the competitive pressure from AMD’s Ryzen "X3D" processors. AMD’s upcoming Ryzen 9 9950X3D2 is expected to feature approximately 208 MB of total cache. Intel’s Nova Lake-S, with its 288 MB configuration, would offer roughly 38% more cache than AMD’s projected flagship.

However, the underlying technologies differ significantly. AMD utilizes 3D die-stacking (TSV technology) to layer a dedicated L3 cache chiplet on top of the compute die. This allows for massive cache sizes without increasing the footprint of the base die. Intel’s bLLC, based on current technical disclosures, appears to be a planar expansion of the cache within the tile or a specialized cache tile integrated via Intel’s Foveros packaging technology. While both methods aim to reduce the "memory wall" bottleneck, Intel’s approach with Nova Lake-S emphasizes a larger integrated pool that may offer different latency characteristics compared to AMD’s stacked solution.

Technical Specifications and Platform Support

Nova Lake-S is expected to debut alongside the LGA 1954 socket, succeeding the LGA 1851 socket used for Arrow Lake. This platform shift is necessary to accommodate the increased power delivery requirements and expanded I/O capabilities of the Series 4 processors. The top-tier 175W models are rumored to require high-end 900-series motherboards to fully unlock their power limits, which could reach up to 350W for single-tile and potentially higher for dual-tile configurations under maximum load.

| Feature | Intel Nova Lake-S | AMD Olympic Ridge (Zen 6) |

|---|---|---|

| Max Cores | 52 (16P + 32E + 4LPE) | 24 (Zen 6) |

| Manufacturing Process | TSMC N2P | TSMC N2P |

| Max Cache (L2+L3) | Up to 320 MB | ~200 MB+ (X3D) |

| Memory Support | DDR5 8000+ MT/s (CUDIMM) | DDR5 7200+ MT/s (CUDIMM) |

| PCIe Lanes | 24 Gen5 (CPU) | TBD |

| Socket | LGA 1954 | AM5 |

| Launch Window | 2H 2026 | 2H 2026 |

The platform will also see a push toward faster memory standards. Intel is optimizing Nova Lake for CUDIMM (Clocked Unbuffered Dual In-Line Memory Modules), with target speeds exceeding 8000 MT/s. This high-speed memory support, combined with the massive bLLC, is intended to create a high-bandwidth, low-latency environment ideal for AI processing, high-frame-rate gaming, and professional content creation.

Historical Context and Development Timeline

The path to Nova Lake has been one of strategic realignment for Intel. Following the challenges faced during the 10nm and 7nm transitions, Intel adopted a "tick-tock" style cadence but with a focus on modularity. Alder Lake (12th Gen) introduced the hybrid architecture, while Meteor Lake and Arrow Lake refined the "tile" or chiplet-based approach.

Nova Lake-S represents the culmination of this modular strategy. By utilizing TSMC’s N2P (2nm-class) process node for the compute tiles, Intel aims to regain the node leadership or parity it lost in previous years. The timeline for Nova Lake-S places its launch in the second half of 2026, setting the stage for a direct confrontation with AMD’s Zen 6 architecture, codenamed "Olympic Ridge."

Broader Market Implications and Industry Reaction

The disclosure of these cache configurations has sent a clear signal to the motherboard and memory industries. Manufacturers like ASUS, MSI, and Gigabyte are likely already in the early stages of designing 900-series boards capable of handling the 175W+ TDP and the complex power phases required for dual-compute tile processors.

For the broader PC market, Intel’s move toward massive cache sizes could redefine performance expectations. If bLLC proves successful in bridging the gaming performance gap created by AMD’s X3D chips, it could lead to a "cache war" where both manufacturers prioritize on-die memory expansion as much as raw clock speeds or core counts. This trend would benefit consumers in the enthusiast space but may also lead to higher MSRPs due to the increased silicon area and packaging complexity required for these massive dies.

Furthermore, the 52-core count on a mainstream desktop platform suggests that the line between "Consumer" and "High-End Desktop" (HEDT) continues to blur. With 52 threads capable of handling massive parallel workloads, Nova Lake-S could potentially cannibalize the lower end of the workstation market, offering professional-grade performance on a standard consumer socket.

As the industry moves toward 2026, the competition between Intel’s Nova Lake and AMD’s Zen 6 will likely be the defining battle of the decade for the x86 ecosystem. With both companies targeting the 2nm node and employing advanced packaging techniques to house enormous cache pools, the next generation of desktop computing promises to deliver a generational leap in performance that has not been seen since the initial introduction of the Ryzen architecture or Intel’s move to hybrid cores. For now, the hardware community remains focused on how these engineering samples will translate into real-world benchmarks once the first silicon hits the testing labs in late 2025.